1.首先安装Codewarrior For Armv8 ,目前最新的版本是CW_CW4NET_v2019.01,安装完成后需要Help->update更新最新的补丁包。

20220925 update: 目前最新的版本是11.5 是CW_CW4NET_v202006版本

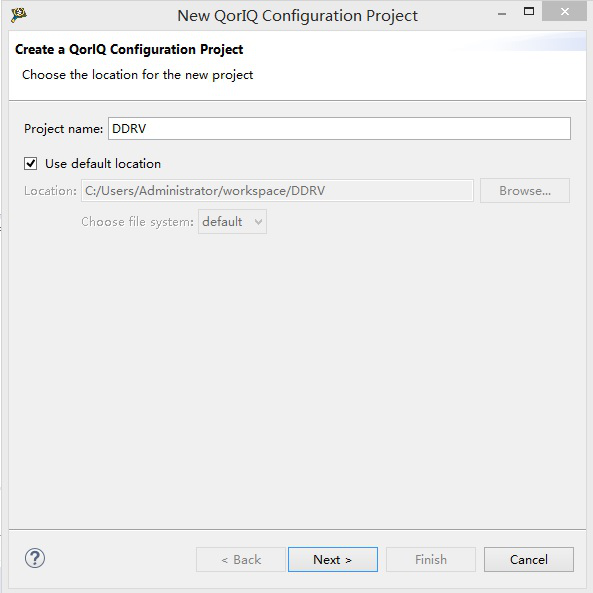

3.输入工程名字和地址,

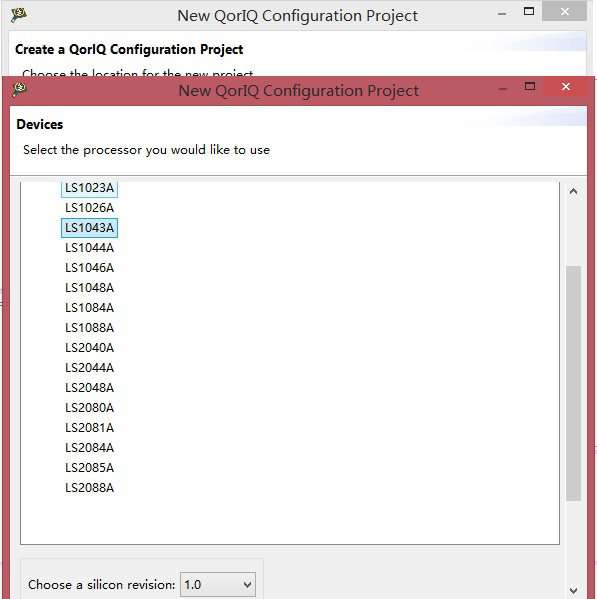

4,因为这个测试采用LS1043ARDB开发板,所以选择LS1043

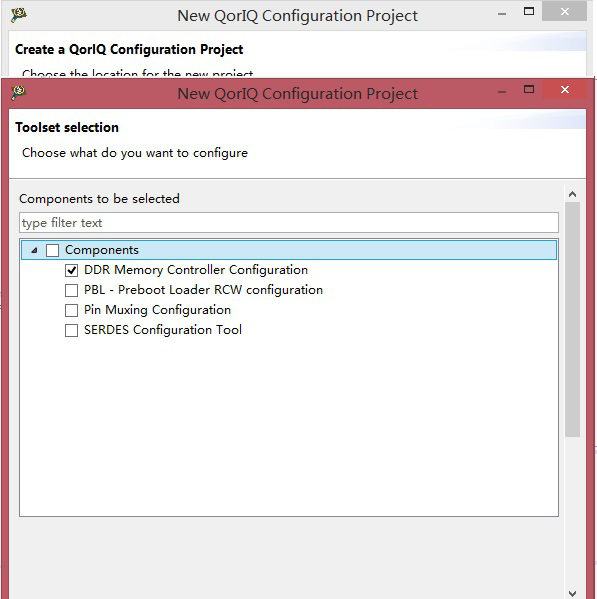

5.选择DDR Memory Controller Configuration

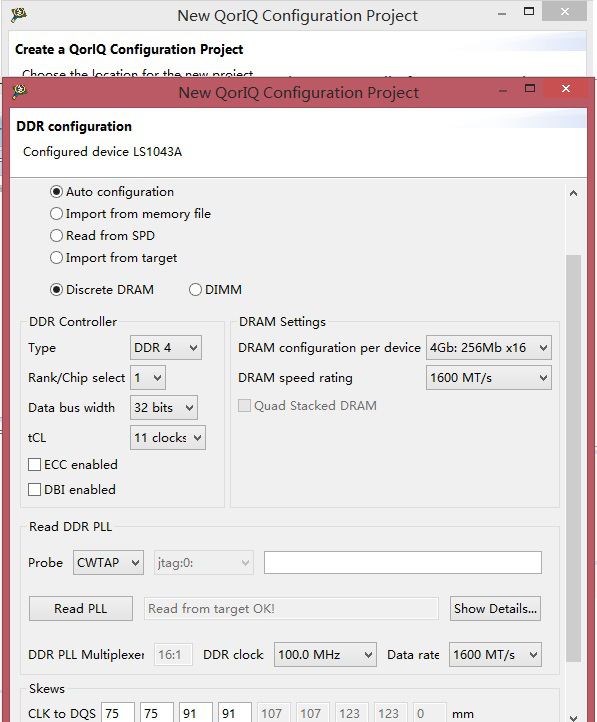

6.DDR4参数选择,Auto Configuration模式,Discrete DRAM,,根据板子上目前所用的DDR参数选择,颗粒容量,运行频率一定要设对。软件会自动根据频率配置基本的时序参数。

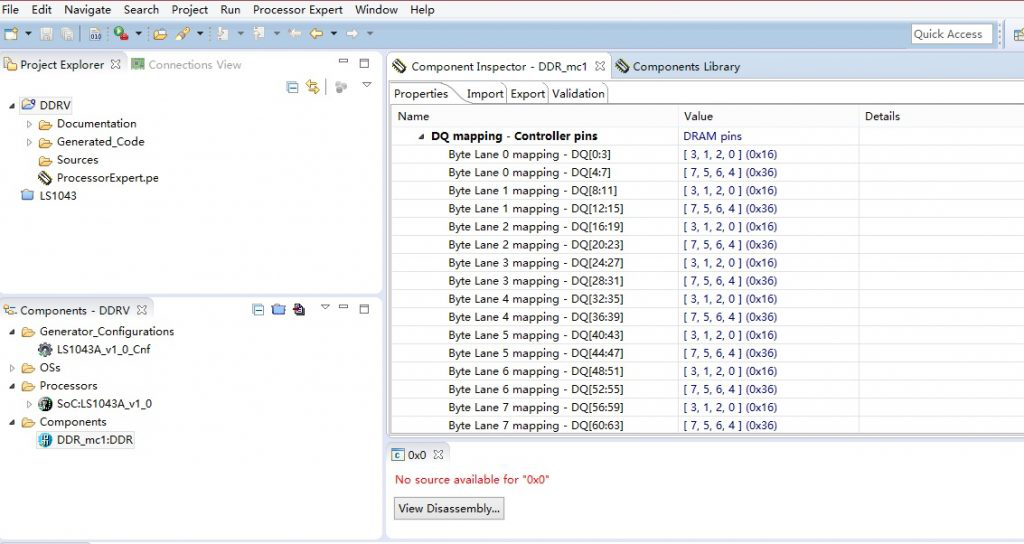

7,点确定后修改DQ mapping配置 ,这个需要根据硬件上DDR跟CPU数据线的联接设计来确定。

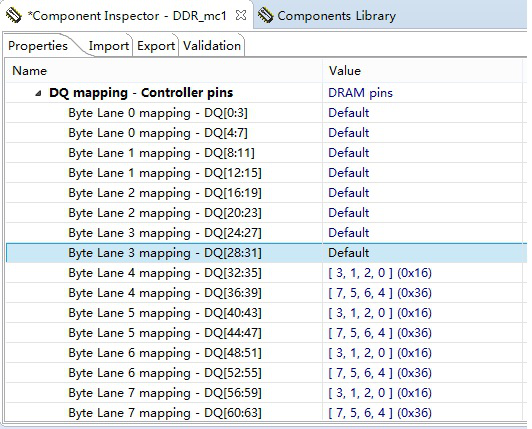

8 LS1043ARDB开发板的DQ mapping的设置如下,因为LS1043采用DDR4颗粒设计,数据线采用一对一设计,所以采用默认值即可。DQ mapping虽然增加了设计灵活性,但是也增加了调试难度,不熟读文档可能都不知道如何配置。

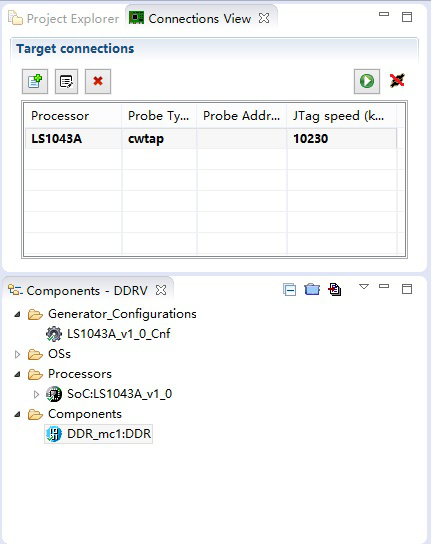

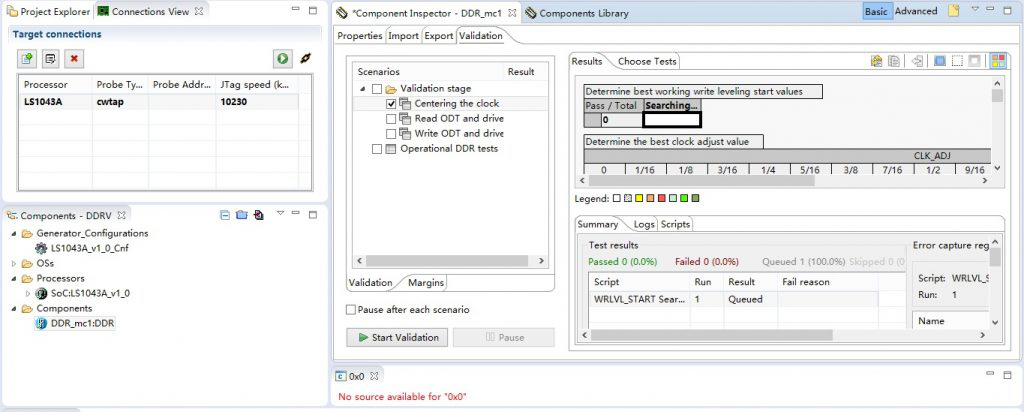

9 Codewarrior tap工具链接方式窗口,点击绿色箭头准备链接开发板。

10 绿色箭头右边的图标说明Codewarrior已经通过codewarrior tap联接上了开发板

11 测试先选Centering the Clock, 开始测试Start Validation

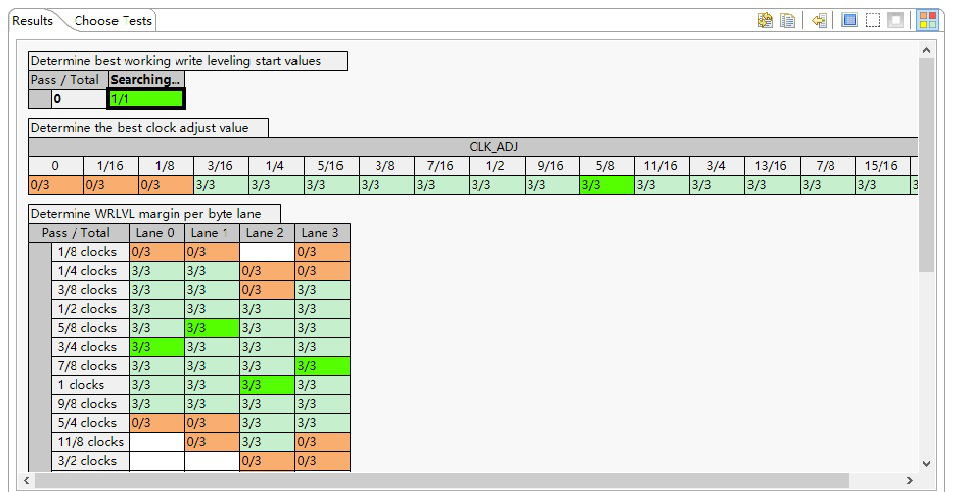

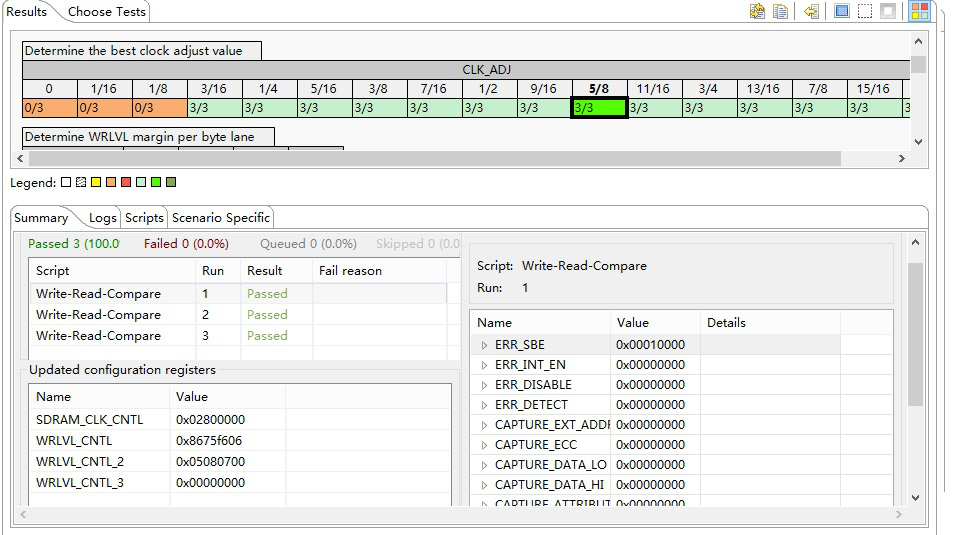

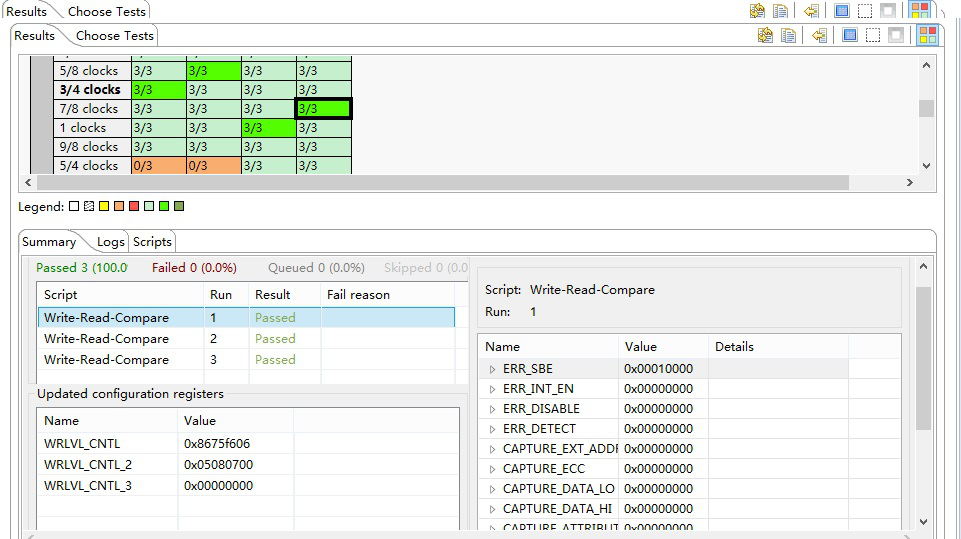

12 跑完测试后如下所示,绿色框说明是推荐的时序配置值。

13,点击绿色框,把配置值记下来,更新到u-boot里,测试完成,

如果要优化ODT值,请做第二和第三项测试。

14 更新u-boot如下:

board/freescale/ls1043ardb/ddr.h文件,针对不同频率跑出来的Writeleveling值要更新到对应的频率行处。

static const struct board_specific_parameters udimm0[] = {

/*

* memory controller 0

* num| hi| rank| clk| wrlvl | wrlvl | wrlvl | cpo |wrdata|2T

* ranks| mhz| GB |adjst| start | ctl2 | ctl3 | |delay |

*/

#ifdef CONFIG_SYS_FSL_DDR4

{1, 1666, 0, 12, 7, 0x07090800, 0x00000000,},

{1, 1900, 0, 12, 7, 0x07090800, 0x00000000,},

{1, 2200, 0, 12, 7, 0x07090800, 0x00000000,},

#endif

Codewarrior tap工具和LS1043ARDB工具网址如下:

参考文档: