一:OK1028开发板介绍,请参考如下网址:https://www.forlinx.com/product/126.html

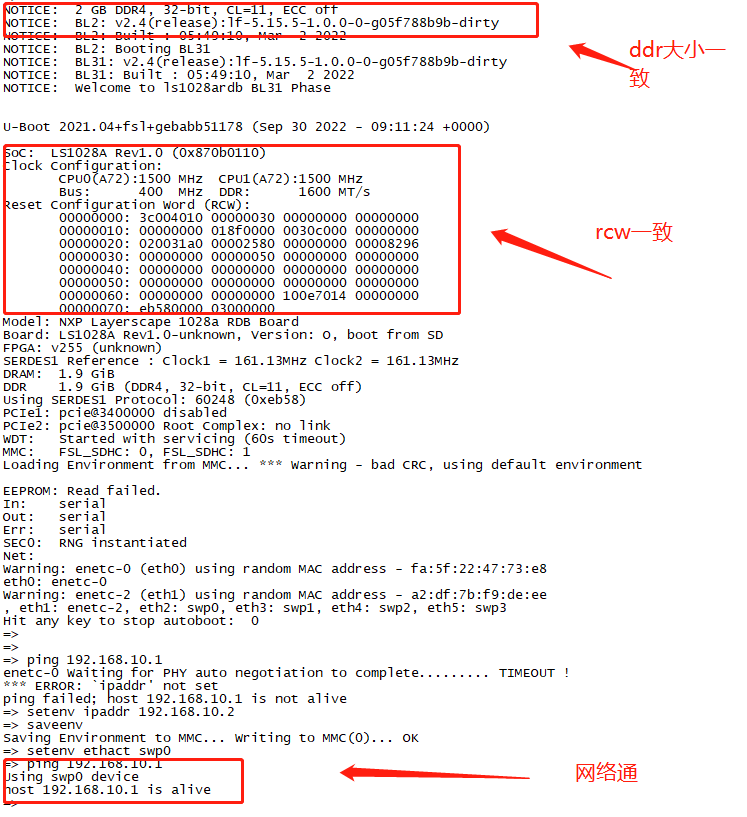

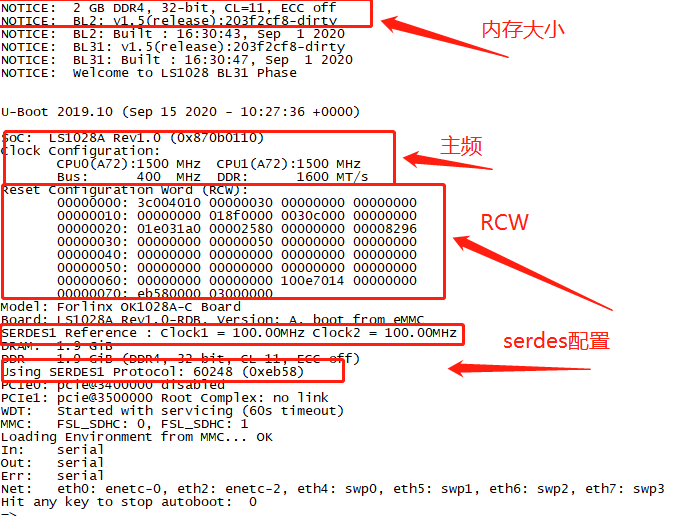

二:根据OK1028 uboot打印信息收集开发板硬件配置:

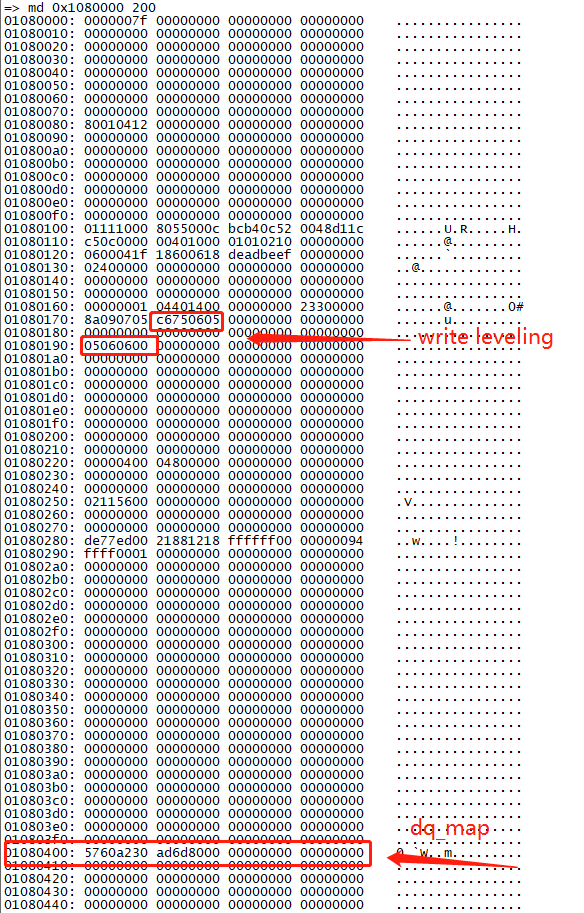

三:md 0x1080000 200 通过此uboot命令收集ddr配置参数:

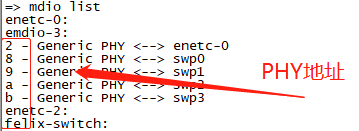

四: mdio list通过此uboot命令收集网口PHY地址信息: QSGMII网口地址为:8,9,a,b

五:修改RCW代码如下:

diff --git a/ls1028ardb/R_SQPP_0x85bb/rcw_1500_gpu600.rcw b/ls1028ardb/R_SQPP_0x85bb/rcw_1500_gpu600.rcw

index 057b0f1..674d9a8 100644

--- a/ls1028ardb/R_SQPP_0x85bb/rcw_1500_gpu600.rcw

+++ b/ls1028ardb/R_SQPP_0x85bb/rcw_1500_gpu600.rcw

@@ -12,7 +12,7 @@

SYS_PLL_RAT=4

MEM_PLL_RAT=16

-CGA_PLL1_RAT=15

+CGA_PLL1_RAT=13

CGA_PLL2_RAT=12

HWA_CGA_M1_CLK_SEL=7

HWA_CGA_M2_CLK_SEL=1

@@ -27,17 +27,20 @@ IIC2_PMUX=6

IIC3_PMUX=2

IIC4_PMUX=2

IIC5_PMUX=1

-IIC6_PMUX=3

+IIC6_PMUX=0

+XSPI1_A_DATA74_PMUX=1

CLK_OUT_PMUX=2

-EC1_SAI4_5_PMUX=5

-EC1_SAI3_6_PMUX=5

+ASLEEP_PMUX=1

+EC1_SAI4_5_PMUX=2

+EC1_SAI3_6_PMUX=1

USB3_CLK_FSEL=39

ENETC_RCW=3

-GTX_CLK125_PMUX=2

+GTX_CLK125_PMUX=1

SRDS_PRTCL_S1_L0=8

SRDS_PRTCL_S1_L1=5

SRDS_PRTCL_S1_L2=11

-SRDS_PRTCL_S1_L3=11

+SRDS_PRTCL_S1_L3=14

+SRDS_S1_REFCLK_SRC_SEL=3

/* Errata for PCIe controller */

#include <../ls1028asi/a008851.rcw>

六: 修改atf代码如下:

diff --git a/plat/nxp/soc-ls1028a/ls1028ardb/ddr_init.c b/plat/nxp/soc-ls1028a/ls1028ardb/ddr_init.c

index 6a65566ba..8d8e4a6a8 100644

--- a/plat/nxp/soc-ls1028a/ls1028ardb/ddr_init.c

+++ b/plat/nxp/soc-ls1028a/ls1028ardb/ddr_init.c

@@ -12,50 +12,50 @@

#ifdef CONFIG_STATIC_DDR

const struct ddr_cfg_regs static_1600 = {

- .cs[0].config = 0x80040422,

- .cs[0].bnds = 0xFF,

- .sdram_cfg[0] = 0xE50C0004,

- .sdram_cfg[1] = 0x401100,

- .timing_cfg[0] = 0x91550018,

- .timing_cfg[1] = 0xBAB40C42,

- .timing_cfg[2] = 0x48C111,

- .timing_cfg[3] = 0x1111000,

- .timing_cfg[4] = 0x2,

- .timing_cfg[5] = 0x3401400,

- .timing_cfg[7] = 0x23300000,

- .timing_cfg[8] = 0x2114600,

- .sdram_mode[0] = 0x3010210,

- .sdram_mode[9] = 0x4000000,

- .sdram_mode[8] = 0x500,

- .sdram_mode[2] = 0x10210,

- .sdram_mode[10] = 0x400,

- .sdram_mode[11] = 0x4000000,

- .sdram_mode[4] = 0x10210,

- .sdram_mode[12] = 0x400,

- .sdram_mode[13] = 0x4000000,

- .sdram_mode[6] = 0x10210,

- .sdram_mode[14] = 0x400,

- .sdram_mode[15] = 0x4000000,

- .interval = 0x18600618,

- .data_init = 0xdeadbeef,

- .zq_cntl = 0x8A090705,

- .clk_cntl = 0x2000000,

- .cdr[0] = 0x80040000,

- .cdr[1] = 0xA181,

- .wrlvl_cntl[0] = 0x8675F605,

- .wrlvl_cntl[1] = 0x6070700,

- .wrlvl_cntl[2] = 0x0000008,

- .dq_map[0] = 0x5b65b658,

- .dq_map[1] = 0xd96d8000,

- .dq_map[2] = 0,

- .dq_map[3] = 0x1600000,

- .debug[28] = 0x00700046,

+ .cs[0].config = 0x80010412,

+ .cs[0].bnds = 0x7F,

+ .sdram_cfg[0] = 0xC50C0000,

+ .sdram_cfg[1] = 0x401000,

+ .timing_cfg[0] = 0x8055000c,

+ .timing_cfg[1] = 0xbcb40c52,

+ .timing_cfg[2] = 0x48d11c,

+ .timing_cfg[3] = 0x1111000,

+ .timing_cfg[4] = 0x1,

+ .timing_cfg[5] = 0x4401400,

+ .timing_cfg[7] = 0x23300000,

+ .timing_cfg[8] = 0x2115600,

+ .sdram_mode[0] = 0x1010210,

+ .sdram_mode[9] = 0x4800000,

+ .sdram_mode[8] = 0x400,

+ .sdram_mode[2] = 0x00,

+ .sdram_mode[10] = 0x00,

+ .sdram_mode[11] = 0x00,

+ .sdram_mode[4] = 0x00,

+ .sdram_mode[12] = 0x00,

+ .sdram_mode[13] = 0x00,

+ .sdram_mode[6] = 0x00,

+ .sdram_mode[14] = 0x00,

+ .sdram_mode[15] = 0x00,

+ .interval = 0x18600618,

+ .data_init = 0xdeadbeef,

+ .zq_cntl = 0x8A090705,

+ .clk_cntl = 0x2400000,

+ .cdr[0] = 0x80080000,

+ .cdr[1] = 0xA180,

+ .wrlvl_cntl[0] = 0x86750605,

+ .wrlvl_cntl[1] = 0x5060600,

+ .wrlvl_cntl[2] = 0x0000000,

+ .dq_map[0] = 0x5760a230,

+ .dq_map[1] = 0xad6d8000,

+ .dq_map[2] = 0x00,

+ .dq_map[3] = 0x00,

+ .debug[28] = 0x00700046,

};

long long board_static_ddr(struct ddr_info *priv)

{

memcpy(&priv->ddr_reg, &static_1600, sizeof(static_1600));

- return 0x100000000ULL;

+ return 0x80000000ULL;

}

#else

diff --git a/plat/nxp/soc-ls1028a/ls1028ardb/plat_def.h b/plat/nxp/soc-ls1028a/ls1028ardb/plat_def.h

index 3f20dc7e0..44ca47926 100644

--- a/plat/nxp/soc-ls1028a/ls1028ardb/plat_def.h

+++ b/plat/nxp/soc-ls1028a/ls1028ardb/plat_def.h

@@ -26,7 +26,6 @@

#define NXP_CONSOLE_BAUDRATE 115200

#define NXP_SPD_EEPROM0 0x51

-

/* Size of cacheable stacks */

#if defined(IMAGE_BL2)

#if defined(TRUSTED_BOARD_BOOT)

diff --git a/plat/nxp/soc-ls1028a/ls1028ardb/platform.mk b/plat/nxp/soc-ls1028a/ls1028ardb/platform.mk

index 122df5553..4769af84a 100644

--- a/plat/nxp/soc-ls1028a/ls1028ardb/platform.mk

+++ b/plat/nxp/soc-ls1028a/ls1028ardb/platform.mk

@@ -14,7 +14,7 @@ WARM_BOOT := no

NUM_OF_DDRC := 1

CONFIG_DDR_NODIMM := 1

DDR_ECC_EN := yes

-

+CONFIG_STATIC_DDR := 1

# On-board flash

FLASH_TYPE := MT35XU02G

XSPI_FLASH_SZ := 0x10000000

七:修改uboot设备树适配网络代码如下:

diff --git a/arch/arm/dts/fsl-ls1028a-rdb.dts b/arch/arm/dts/fsl-ls1028a-rdb.dts

index 3432fca352..d6ede6f54f 100644

--- a/arch/arm/dts/fsl-ls1028a-rdb.dts

+++ b/arch/arm/dts/fsl-ls1028a-rdb.dts

@@ -185,19 +185,19 @@

};

/* VSC8514 QSGMII PHY */

- sw_phy0: phy@10 {

- reg = <0x10>;

+ sw_phy0: phy@8 {

+ reg = <0x8>;

};

- sw_phy1: phy@11 {

- reg = <0x11>;

+ sw_phy1: phy@9 {

+ reg = <0x9>;

};

- sw_phy2: phy@12 {

- reg = <0x12>;

+ sw_phy2: phy@a {

+ reg = <0xa>;

};

- sw_phy3: phy@13 {

- reg = <0x13>;

+ sw_phy3: phy@b {

+ reg = <0xb>;

};

};

八:修改liniux设备树适配网络代码如下:

iff --git a/arch/arm64/boot/dts/freescale/fsl-ls1028a-rdb.dts b/arch/arm64/boot/dts/freescale/fsl-ls1028a-rdb.dts

index 1b6497808d0f..9454c36b5678 100644

--- a/arch/arm64/boot/dts/freescale/fsl-ls1028a-rdb.dts

+++ b/arch/arm64/boot/dts/freescale/fsl-ls1028a-rdb.dts

@@ -199,20 +199,20 @@ &duart1 {

&enetc_mdio_pf3 {

/* VSC8514 QSGMII quad PHY */

- qsgmii_phy0: ethernet-phy@10 {

- reg = <0x10>;

+ qsgmii_phy0: ethernet-phy@8 {

+ reg = <0x8>;

};

- qsgmii_phy1: ethernet-phy@11 {

- reg = <0x11>;

+ qsgmii_phy1: ethernet-phy@9 {

+ reg = <0x9>;

};

- qsgmii_phy2: ethernet-phy@12 {

- reg = <0x12>;

+ qsgmii_phy2: ethernet-phy@10 {

+ reg = <0xa>;

};

- qsgmii_phy3: ethernet-phy@13 {

- reg = <0x13>;

+ qsgmii_phy3: ethernet-phy@11 {

+ reg = <0xb>;

};

};

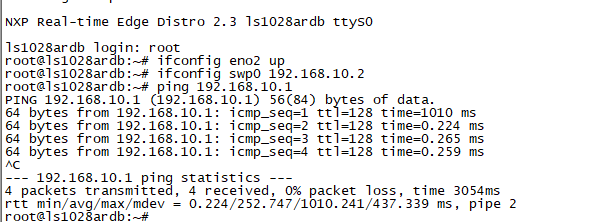

启动界面: